OpenloTSummit Europe

# Embedded Linux on RISC-V

Khem Raj

# Agenda

- Introduction

- Upstream Status

- What works

- Work in progress

- Q/A

# RISC-V (risk-five)

- "Fifth" RISC ISA from Berkeley

- 32, 64 and 128 bits wide instruction sets

- little-endian by default

- Specifications

- https://riscv.org/specifications/

- RV32I and RV64I + Extensions

- M Integer Mult/Div

- A Atomic Memory access

- F Floating point ( single precision )

- D Floating point ( Double precision )

- C Compressed

- Concatenate to represent ISA

- E.g. RV64IMAFD

- 'G' is abbreviation for 'IMAFD"

- RV64GC is generally supported ISA by major distros e.g. (Fedora, Debian, ...)

- Non-standard extensions begin with 'X'

- E.g. RV64GXargle\_Xbargle

### Tools

- Binutils 2.28

- GCC 7.0

- GLIBC 2.27

- Rv32i 2.28

- Newlib 3.0.0

- Qemu 2.12.0

- GDB 8.2

- Baremetal support only

- riscv\*-\*-elf

### GNU Binutils 2.28 Released, Adds RISC-V Support

Written by Michael Larabel in GNU on 6 March 2017 at 11:18 AM EST. 2 Comments

Binutils 2.28 is out today as the latest version of this important GNU package.

Binutils 2.28 brings new options (--remove-relocations=SECTIONPATTERN and nm --with-version-strings), improvements to the ARC and PowerPC ports, Gas adds support for the RISC-V architecture, Gas also now supports the Cortex-M23 and Cortex-M33 processors, and GNU Id also adds RISC-V support, and other new options. The RISC-V architecture support

was also recently merged for the GCC 7 compiler stack.

### RISC-V Port Lands In GCC 7 Codebase

Written by Michael Larabel in GNU on 6 February 2017 at 05:18 PM EST. 4 Comments

Last month the RISC-V GCC port was approved for landing in GCC 7 while today that merge finally happened.

The RISC-V GCC port has been a work in progress for a long time and was held up by university lawyers while that was all cleared up, the code went through a few rounds of code revisions, and the steering committee approved landing RISC-V support even as the codebase

has moved onto only bug/regression fixes. Today all of that code finally was merged into the GCC7 code-base.

### RISC-V SW Dev > Newlib 3.0.0 released with RISC-V support 6 posts by 5 authors ©

### Title Gilein

ni ioiks.

newlib 3.0 was released last week[1]. It's first official release with RISC-V support, you can found that in their ftp[2], and read more new changes from their NEWS file[3]:)

- [1] https://sourceware.org/ml/newlib/2018/msg00019.html

- [2] ftp://sourceware.org/pub/newlib/index.html

- [3] https://sourceware.org/git/gitweb.cgi?p=newlib-cygwin.git;a=blob\_plain;f=newlib/NEWS;hb=HEAD

### **Boot Loaders**

- Coreboot

- Supports RISC-V upstream

- U-Boot 2018.11

- RISC-V virt board

- Support is Upstream

- PK/BBL (Proxy Kernel/Berkeley Boot Loader)

- https://github.com/riscv/riscv-pk

### RISC-V Linux Kernel Port

- Stable ABI in upstream since 4.15

- 4.19 contains drivers for Qemu "virt" board

- Major Contributors

# Operating Systems -Zephyr

- https://docs.zephyrproject.org/latest/boards/riscv32/index.html

- SiFive HiFive1

- Microsemi M2GL025 Mi-V

- RISCV32 Emulation (QEMU)

- Zedboard Pulpino

- Released in 1.13.0

- Now Included in Standard SDK releases

### Distribution Ports – cross-distro Defaults

- Uses RV64GC LP64 ABI

- Little-Endian

- Embedded Linux Distributions

- Have RV32I ABI variants

- More...

### Operating Systems - Fedora

- https://fedoraproject.org/wiki/Architectures/RISC-V

- Instruction of installation:

- https://fedoraproject.org/wiki/Architectures/RISC-V/Installing

- Info about Bootstrapping and Building

- Bootstrap finished in March'18

- Koji build farm is up

- Fedora 29/Rawhide packages building using koji

- http://fedora-riscv.tranguillity.se/koji/

- Self-hosted

- HiFive Unleashed

- QEMU

### Operating Systems - Debian

https://wiki.debian.org/RISC-V

### OpenEmbedded/Yocto

- First RISC-V Linux Distro

- https://riscv.org/2015/01/a-linux-distribution-for-risc-v/

- Poky Fork (yocto Project Reference Distro)

- Core Support up-streamed 2.5 release

- BSP/Architecture Layer (meta-riscv)

- https://github.com/riscv/meta-riscv

- QEMU machine

- SiFive Freedom U540

- Application Development Cross SDK

- On device SDK

- Baremetal rv32 and rv64 targets

- Generates bare-metal SDKs useful for RTOSes e.g. zephyr

- Current Tuning

- RV32, RV64

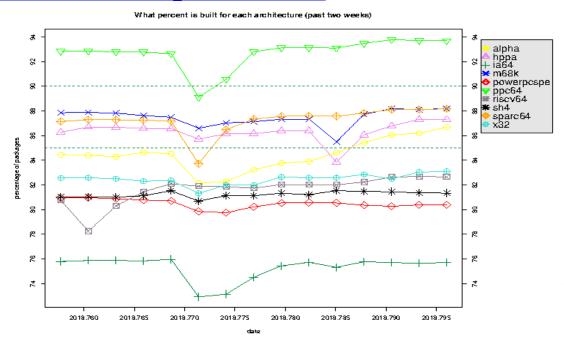

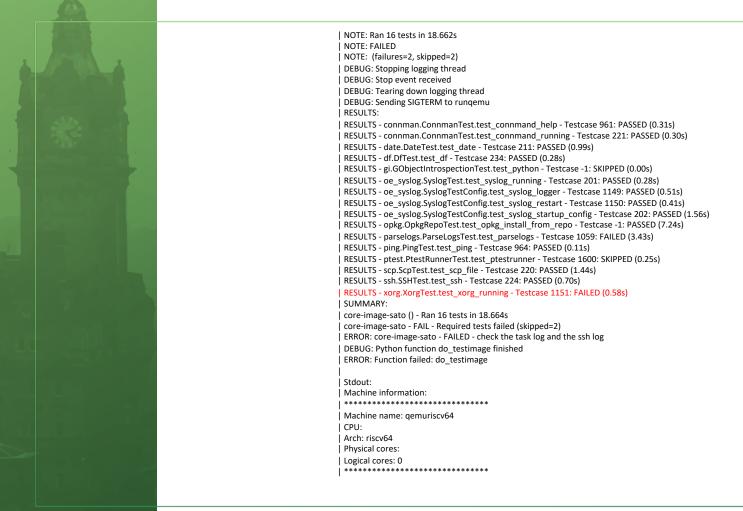

- Continuous Integration

- In progress

- World Builds

- http://errors.yoctoproject.org/Errors/Build/70151/

### 38 errors for Build #70151

|                   |            |                                            |              |        |             | Edit colum | ns 🕶 S  | Show rows: | 25 ‡   |

|-------------------|------------|--------------------------------------------|--------------|--------|-------------|------------|---------|------------|--------|

| Submitted on ▼    | Error type | Failure                                    | Machine      | Distro | Host distro | Branch     | Commit  |            | Simila |

| 21/10/18<br>14:29 | Recipe     | gstreamer1.0: do_compile                   | qemuriscv64  | yoe    | arch/arch   | yoe/mut    | b7c5ac5 |            | 0      |

| 21/10/18<br>14:29 | Recipe     | gstreamer: do_configure                    | qemuriscv64  | yoe    | arch/arch   | yoe/mut    | b7c5ac5 |            | 3      |

| 21/10/18<br>14:29 | Recipe     | rust-cross-riscv64:<br>do_rust_gen_targets | qemuriscv64  | yoe    | arch/arch   | yoe/mut    | b7c5ac5 |            | 0      |

| 21/10/18<br>14:29 | Recipe     | python-greenlet: do_compile                | qemuriscv64  | yoe    | arch/arch   | yoe/mut    | b7c5ac5 |            | 4      |

| 21/10/18<br>14:29 | Recipe     | libgit2-native: do_configure               | qemuriscv64  | yoe    | arch/arch   | yoe/mut    | b7c5ac5 |            | 0      |

|                   |            |                                            | quituriscror | ,      |             | , comut    | D7c5ac  | •<br>TL    |        |

### Buildroot

- https://github.com/riscv/riscv-buildroot

- Use 'riscv-start' branch

- Submitted Upstream

- http://lists.busybox.net/pipermail/buildroot/201

8-September/230689.html

- RV32 port

- Submitted

- RISC-V LLVM

- https://github.com/lowRISC/riscv-llvm

- Experimental support is up-streamed

- Full patch-set upstreaming is going on

- LLD port has been submitted

- Musl C library support

- https://github.com/riscv/riscv-musl

- Upstream submission Under Review

- https://www.openwall.com/lists/musl/2018/09/28/1

- OpenOCD

- Out of tree <a href="http://github.com/riscv/riscv-openocd">http://github.com/riscv/riscv-openocd</a>

- Multi-core, 64-bit

- GDB (Linux)

- UEFI

- Grub

- V8

- Node.js

- Rust

### Contributions

- Unique Contributors to Linux arch ports (4.18)

- X86 1908

- ARM 3053

- MIPS 906

- PPC 1462

- RISCV 31 --> We need to get this number up

### Find out more !!!

- Latest Software Status

- https://riscv.org/software-status/

- Cores and SOCs overview

- <u>https://riscv.org/risc-v-cores/</u>

- Mailing List

- linux-riscv@lists.infradead.org

### Get Involved

- Standards work (ABI, spec etc.)

- Improve/upstream Linux distribution support

- Port more software packages to RISC-V

- Most Software is Upstream!

- Use a project's regular communication mechanisms

- Specific to RISC-V

- https://github.com/riscv/: Contains in-progress ports

- sw-dev@groups.riscv.org: Software discussion

- <u>patches@groups.riscv.org</u>: Patches to RISC-V ports

- #riscv on Freenode: General RISC-V discussion

- <u>linux-riscv@lists.infradead.org</u>: RISC-V Linux Port

- Stack Overflow

- https://stackoverflow.com/questions/tagged/riscv

### More on RISC-V @ ELCE 2018

Monday, October 22 • 18:00 - 18:40

BoF: RISC-V SW Ecosystem Status and Needs - Atish Patra, Western Digital; Olof

Johansson, Palmer Dabbelt & Paul Walmsley, RISC-V

### Seeds of Change (Some 25+ years ago)

- https://groups.google.com/forum/#!msg/comp. os.minix/dlNtH7RRrGA/SwRavCzVE7gJ

- 22M+ Lines of Code

- 14K+ contributors

- Unprecedented Development Velocity

- Most Successful Open Source Software Project

### comp.os.minix >

What would you like to see most in minix?

Hello everybody out there using minix -

Linus Benedict Torvalds

I'm doing a (free) operating system (just a hobby, won't be big and professional like gnu) for 386(486) AT clones. This has been brewing since april, and is starting to get ready. I'd like any feedback on things people like/dislike in minix, as my OS resembles it somewhat (same physical layout of the file-system (due to practical reasons) among other things).

I've currently ported bash(1.08) and gcc(1.40), and things seem to work. This implies that I'll get something practical within a few months, and I'd like to know what features most people would want. Any suggestions are welcome, but I won't promise I'll implement them:

Linus (torv...@kruuna.helsinki.fi)

PS. Yes - it's free of any minix code, and it has a multi-threaded fs. It is NOT protable (uses 386 task switching etc), and it probably never will support anything other than AT-harddisks, as that's all I have :-(.

## History Tends to repeat ©

Usually when forgotten

But sometimes to build upon proven ways

# Thank you

Khem Raj <raj.khem@gmail.com>